### **TMS320C4x**

# User's Guide

User's Guide

**TMS320C4x**

1999

## TMS320C4x User's Guide

SPRU063C May 1999

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

#### **Preface**

### **Read This First**

#### About This Manual

This user's guide serves as a reference book for the TMS320C40 and TMS320C44 digital signal processors. Throughout the book, all references to the TMS320C4x apply to both devices, except when otherwise noted.

#### How to Use This Manual

The following table summarizes the information contained in this user's guide:

| If you are looking for information about: | Turn to these chapters:                              |

|-------------------------------------------|------------------------------------------------------|

| Addressing modes                          | Chapter 6, Addressing Modes                          |

| ARAUs                                     | Chapter 2, Architectural Overview                    |

| Bootloader                                | Chapter 10, The Bootloader                           |

| Bus Structure                             | Chapter 2, Architectural Overview                    |

|                                           | Chapter 9, External Bus Operation                    |

| Cache                                     | Chapter 4, Memory and the Instruction Cache          |

| Communication Ports                       | Chapter 12, Communication Ports                      |

| CPU Architecture                          | Chapter 2, Architectural Overview                    |

|                                           | Chapter 3, CPU Registers                             |

| DMA                                       | Chapter 11, The DMA Coprocessor                      |

| Data Formats                              | Chapter 5, Data Formats and Floating-Point Operation |

| Delayed Branches                          | Chapter 7, Program Flow Control                      |

| Instruction set                           | Chapter 14, Assembly Language Instructions           |

| If you are looking for information about: | Turn to these chapters:                     |

|-------------------------------------------|---------------------------------------------|

| Interrupts                                | Chapter 7, Program Flow Control             |

| Memory                                    | Chapter 2, Architectural Overview           |

|                                           | Chapter 4, Memory and the Instruction Cache |

| Peripherals                               | Chapter 12, Communication Ports             |

|                                           | Chapter 11, The DMA Coprocessor             |

|                                           | Chapter 13, <i>Timers</i>                   |

| Overview of the 'C4x                      | Chapter 1, Introduction                     |

| Program control                           | Chapter 7, Program Flow Control             |

| Pipeline                                  | Chapter 8, Pipeline Operation               |

| Registers                                 | Chapter 3, CPU Registers                    |

|                                           | Chapter 12, Communication Ports             |

|                                           | Chapter 11, The DMA Coprocessor             |

|                                           | Chapter 13, <i>Timers</i>                   |

| Repeat Mode                               | Chapter 7, Program Flow Control             |

| Reset                                     | Chapter 7, Program Flow Control             |

| Timers                                    | Chapter 13, <i>Timers</i>                   |

| Traps                                     | Chapter 7, Program Flow Control             |

#### Style and Symbol Conventions

This document uses the following conventions:

Program listings, program examples, file names, and symbol names are shown in a special font. Examples use a bold version of the special font for emphasis. Here is a sample program listing segment:

```

*

LOOP1 RPTB MAX

CMPF *AR0,R0 ;Compare number to the maximum

MAX LDFLT *AR0,R0 ;If greater, this is a new max

B NEXT

LOOP2 RPTB MIN

CMPF *AR0++(1),R0 ;Compare number to the minimum

MIN LDFLT *-AR0(1),R0 ;If smaller, this is new minimum

NEXT .

```

iv

| In syntax descriptions, the instruction is in <b>bold face</b> and the parameters are in <i>italic face</i> . Portions of a syntax that are in <b>bold face</b> should be entered as shown; portions of a syntax that are in <i>italic face</i> describe the <i>type</i> of information that should be entered. Here is an example of an instruction: |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMPF3 src2,src1                                                                                                                                                                                                                                                                                                                                       |

| Notice that although the instruction mnemonic (CMPF3 in this example) is in capital letters, the 'C4x assembler <b>is not case sensitive</b> — it can assemble mnemonics entered in either upper or lower case.                                                                                                                                       |

| $ \textbf{CMPF3} \ \text{is the instruction mnemonic. This instruction has two parameters, indicated by } \textit{src2} \ \text{and } \textit{src1}. $                                                                                                                                                                                                |

| Square brackets ( [ and ] ) identify an optional parameter. If you use an optional parameter, you must specify the information within the brackets; however, you don't enter the brackets themselves. Here's an example of an instruction that has an optional parameter:                                                                             |

| [label] LDP src [,DP]                                                                                                                                                                                                                                                                                                                                 |

| The <b>LDP</b> instruction is shown with two parameters; one is optional. The first parameter, <i>src</i> , is required. The second parameter, <i>DP</i> , and the label, are optional. As this syntax shows, if you use the optional second parameter, you must precede it with a comma.                                                             |

| Throughout this book MSB indicates the most significant bit and LSB indicates the least significant bit. MS indicates the most significant byte and LS indicates the least significant byte.                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                       |

#### Information About Cautions and Warnings

This book may contain cautions and warnings.

This is an example of a caution statement.

A caution statement describes a situation that could potentially damage your software or equipment.

This is an example of a warning statement.

A warning statement describes a situation that could potentially cause harm to <u>you</u>.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

#### Related Documentation From Texas Instruments

The following books describe the TMS320 floating-point devices and related support tools. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800) 477–8924. When ordering, please identify the book by its title and literature number.

- **TMS320C4x General-Purpose Applications User's Guide** (literature number SPRU159) describes software and hardware applications for the 'C4x processor. Also includes development support information, parts lists, and XDS510 emulator design considerations.

- **TMS320C4x** Parallel Processing Development System Technical Reference (literature number SPRU075) describes the TMS320C4x parallel processing system, a system with four C4xs with shared and distributed memory.

- **Parallel Processing with the TMS320C4x** (literature number SPRA031) describes parallel processing and how the 'C4x can be used in parallel processing. Also provides sample parallel processing applications.

- TMS320 Floating-Point DSP Assembly Language Tools User's Guide (literature number SPRU035) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for the 'C3x and 'C4x generations of devices.

- TMS320 Floating-Point DSP Optimizing C Compiler User's Guide (literature number SPRU034) describes the TMS320 floating-point C compiler. This C compiler accepts ANSI standard C source code and produces TMS320 assembly language source code for the 'C3x and 'C4x generations of devices.

- TMS320C4x C Source Debugger User's Guide (literature number SPRU054) tells you how to invoke the 'C4x emulator and simulator versions of the C source debugger interface. This book discusses various aspects of the debugger interface, including window management, command entry, code execution, data management, and breakpoints. It also includes a tutorial that introduces basic debugger functionality.

- **TMS320C4x Technical Brief** (literature number SPRU076) gives a condensed overview of the 'C4x DSP and its development tools. It also lists TMS320C4x third parties.

- TMS320 Family Development Support Reference Guide (literature number SPRU011) describes the '320 family of digital signal processors and the various products that support it. This includes code-generation tools (compilers, assemblers, linkers, etc.) and system integration and debug tools (simulators, emulators, evaluation modules, etc.). This book also lists related documentation, outlines seminars and the university program, and gives factory repair and exchange information.

- **TMS320** Third-Party Support Reference Guide (literature number SPRU052) alphabetically lists over 100 third parties that supply various products that serve the family of '320 digital signal processors—software and hardware development tools, speech recognition, image processing, noise cancellation, modems, etc.

- **TMS320 DSP Designer's Notebook: Volume 1 (SPRT125).** Presents solutions to common design problems using 'C2x, 'C3x, 'C4x, 'C5x, and other TI DSPs.

#### Related Articles and Books

A wide variety of related documentation is available on digital signal processing. These references fall into one of the following application categories:

|        | General-Purpose DSF |

|--------|---------------------|

|        | Graphics/Imagery    |

|        | Speech/Voice        |

|        | Control             |

|        | Multimedia          |

|        | Military            |

|        | Telecommunications  |

|        | Automotive          |

|        | Consumer            |

|        | Medical             |

| $\neg$ | Development Support |

In the following list, references appear in alphabetical order according to author. The documents contain beneficial information regarding designs, operations, and applications for signal-processing systems; all of the documents provide additional references. Texas Instruments strongly suggests that you refer to these publications.

#### General-Purpose DSP:

1) Antoniou, A., *Digital Filters: Analysis and Design*, New York, NY: McGraw-Hill Company, Inc., 1979.

- 2) Brigham, E.O., *The Fast Fourier Transform*, Englewood Cliffs, NJ: Prentice-Hall, Inc., 1974.

- 3) Burrus, C.S., and T.W. Parks, *DFT/FFT and Convolution Algorithms*, New York, NY: John Wiley and Sons, Inc., 1984.

- Chassaing, R., Horning, D.W., "Digital Signal Processing with Fixed and Floating-Point Processors." CoED, USA, Volume 1, Number 1, pages 1–4, March 1991.

- 5) Defatta, David J., Joseph G. Lucas, and William S. Hodgkiss, *Digital Signal Processing: A System Design Approach*, New York: John Wiley, 1988.

- Erskine, C., and S. Magar, "Architecture and Applications of a Second-Generation Digital Signal Processor." Proceedings of IEEE International Conference on Acoustics, Speech, and Signal Processing, USA, 1985.

- Essig, D., C. Erskine, E. Caudel, and S. Magar, "A Second-Generation Digital Signal Processor." *IEEE Journal of Solid-State Circuits*, USA, Volume SC–21, Number 1, pages 86–91, February 1986.

- 8) Frantz, G., K. Lin, J. Reimer, and J. Bradley, "The Texas Instruments TMS320C25 Digital Signal Microcomputer." *IEEE Microelectronics*, USA, Volume 6, Number 6, pages 10–28, December 1986.

- Gass, W., R. Tarrant, T. Richard, B. Pawate, M. Gammel, P. Rajasekaran, R. Wiggins, and C. Covington, "Multiple Digital Signal Processor Environment for Intelligent Signal Processing." *Proceedings of the IEEE,* USA, Volume 75, Number 9, pages 1246–1259, September 1987.

- Gold, Bernard, and C.M. Rader, *Digital Processing of Signals*, New York, NY: McGraw-Hill Company, Inc., 1969.

- 11) Hamming, R.W., *Digital Filters*, Englewood Cliffs, NJ: Prentice-Hall, Inc., 1977.

- 12) IEEE ASSP DSP Committee (Editor), *Programs for Digital Signal Processing*, New York, NY: IEEE Press, 1979.

- 13) Jackson, Leland B., *Digital Filters and Signal Processing*, Hingham, MA: Kluwer Academic Publishers, 1986.

- 14) Jones, D.L., and T.W. Parks, *A Digital Signal Processing Laboratory Using the TMS32010*, Englewood Cliffs, NJ: Prentice-Hall, Inc., 1987.

- 15) Lim, Jae, and Alan V. Oppenheim, *Advanced Topics in Signal Processing*, Englewood Cliffs, NJ: Prentice- Hall, Inc., 1988.

- 16) Lin, K., G. Frantz, and R. Simar, Jr., "The TMS320 Family of Digital Signal Processors." *Proceedings of the IEEE*, USA, Volume 75, Number 9, pages 1143–1159, September 1987.

- 17) Lovrich, A., Reimer, J., "An Advanced Audio Signal Processor." Digest of Technical Papers for 1991 International Conference on Consumer Electronics, June 1991.

- Magar, S., D. Essig, E. Caudel, S. Marshall and R. Peters, "An NMOS Digital Signal Processor with Multiprocessing Capability." *Digest of IEEE International Solid-State Circuits Conference*, USA, February 1985.

- 19) Morris, Robert L., *Digital Signal Processing Software*, Ottawa, Canada: Carleton University, 1983.

- 20) Oppenheim, Alan V. (Editor), *Applications of Digital Signal Processing*, Englewood Cliffs, NJ: Prentice-Hall, Inc., 1978.

- 21) Oppenheim, Alan V., and R.W. Schafer, *Digital Signal Processing*, Englewood Cliffs, NJ: Prentice-Hall, Inc., 1975 and 1988.

- 22) Oppenheim, A.V., A.N. Willsky, and I.T. Young, *Signals and Systems*, Englewood Cliffs, NJ: Prentice-Hall, Inc., 1983.

- Papamichalis, P.E., and C.S. Burrus, "Conversion of Digit-Reversed to Bit-Reversed Order in FFT Algorithms." *Proceedings of ICASSP 89*, USA, pages 984–987, May 1989.

- 24) Papamichalis, P., and R. Simar, Jr., "The TMS320C30 Floating-Point Digital Signal Processor." *IEEE Micro Magazine*, USA, pages 13–29, December 1988.

- 25) Parks, T.W., and C.S. Burrus, *Digital Filter Design*, New York, NY: John Wiley and Sons, Inc., 1987.

- 26) Peterson, C., Zervakis, M., Shehadeh, N., "Adaptive Filter Design and Implementation Using the TMS320C25 Microprocessor." Computers in Education Journal, USA, Volume 3, Number 3, pages 12–16, July–September 1993.

- 27) Prado, J., and R. Alcantara, "A Fast Square-Rooting Algorithm Using a Digital Signal Processor." *Proceedings of IEEE*, USA, Volume 75, Number 2, pages 262–264, February 1987.

- 28) Rabiner, L.R. and B. Gold, *Theory and Applications of Digital Signal Processing*, Englewood Cliffs, NJ: Prentice-Hall, Inc., 1975.

- 29) Simar, Jr., R., and A. Davis, "The Application of High-Level Languages to Single-Chip Digital Signal Processors." *Proceedings of ICASSP 88*, USA, Volume D, page 1678, April 1988.

- 30) Simar, Jr., R., T. Leigh, P. Koeppen, J. Leach, J. Potts, and D. Blalock, "A 40 MFLOPS Digital Signal Processor: the First Supercomputer on a Chip." Proceedings of ICASSP 87, USA, Catalog Number 87CH2396–0, Volume 1, pages 535–538, April 1987.

- 31) Simar, Jr., R., and J. Reimer, "The TMS320C25: a 100 ns CMOS VLSI Digital Signal Processor." 1986 Workshop on Applications of Signal Processing to Audio and Acoustics, September 1986.

- 32) Texas Instruments, *Digital Signal Processing Applications with the TMS320 Family*, 1986; Englewood Cliffs, NJ: Prentice-Hall, Inc., 1987.

- 33) Treichler, J.R., C.R. Johnson, Jr., and M.G. Larimore, *A Practical Guide to Adaptive Filter Design*, New York, NY: John Wiley and Sons, Inc., 1987.

#### Graphics/Imagery:

- 1) Andrews, H.C., and B.R. Hunt, *Digital Image Restoration*, Englewood Cliffs, NJ: Prentice-Hall, Inc., 1977.

- 2) Gonzales, Rafael C., and Paul Wintz, *Digital Image Processing*, Reading, MA: Addison-Wesley Publishing Company, Inc., 1977.

- 3) Papamichalis, P.E., "FFT Implementation on the TMS320C30." *Proceedings of ICASSP 88*, USA, Volume D, page 1399, April 1988.

- 4) Pratt, William K., *Digital Image Processing*, New York, NY: John Wiley and Sons, 1978.

- 5) Reimer, J., and A. Lovrich, "Graphics with the TMS32020." WESCON/85 Conference Record, USA, 1985.

#### Speech/Voice:

- DellaMorte, J., and P. Papamichalis, "Full-Duplex Real-Time Implementation of the FED-STD-1015 LPC-10e Standard V.52 on the TMS320C25." Proceedings of SPEECH TECH 89, pages 218–221, May 1989.

- Frantz, G.A., and K.S. Lin, "A Low-Cost Speech System Using the TMS320C17." Proceedings of SPEECH TECH '87, pages 25–29, April 1987.

- 3) Gray, A.H., and J.D. Markel, *Linear Prediction of Speech*, New York, NY: Springer-Verlag, 1976.

- 4) Jayant, N.S., and Peter Noll, *Digital Coding of Waveforms*, Englewood Cliffs, NJ: Prentice-Hall, Inc., 1984.

- 5) Papamichalis, Panos, *Practical Approaches to Speech Coding*, Englewood Cliffs, NJ: Prentice-Hall, Inc., 1987.

- 6) Papamichalis, P., and D. Lively, "Implementation of the DOD Standard LPC–10/52E on the TMS320C25." *Proceedings of SPEECH TECH '87*, pages 201–204, April 1987.

- Pawate, B.I., and G.R. Doddington, "Implementation of a Hidden Markov Model-Based Layered Grammar Recognizer." *Proceedings of ICASSP* 89, USA, pages 801–804, May 1989.

- 8) Rabiner, L.R., and R.W. Schafer, *Digital Processing of Speech Signals*, Englewood Cliffs, NJ: Prentice-Hall, Inc., 1978.

- 9) Reimer, J.B. and K.S. Lin, "TMS320 Digital Signal Processors in Speech Applications." *Proceedings of SPEECH TECH '88*, April 1988.

- Reimer, J.B., M.L. McMahan, and W.W. Anderson, "Speech Recognition for a Low-Cost System Using a DSP." Digest of Technical Papers for 1987 International Conference on Consumer Electronics, June 1987.

#### Control:

- 1) Ahmed, I., "16-Bit DSP Microcontroller Fits Motion Control System Application." *PCIM*, October 1988.

- Ahmed, I., "Implementation of Self Tuning Regulators with TMS320 Family of Digital Signal Processors." MOTORCON '88, pages 248–262, September 1988.

- Ahmed, I., and S. Lindquist, "Digital Signal Processors: Simplifying High-Performance Control." *Machine Design*, September 1987.

- 4) Ahmed, I., and S. Meshkat, "Using DSPs in Control." *Control Engineering*, February 1988.

- 5) Allen, C. and P. Pillay, "TMS320 Design for Vector and Current Control of AC Motor Drives." *Electronics Letters*, UK, Volume 28, Number 23, pages 2188–2190, November 1992.

- 6) Bose, B.K., and P.M. Szczesny, "A Microcomputer-Based Control and Simulation of an Advanced IPM Synchronous Machine Drive System for Electric Vehicle Propulsion." *Proceedings of IECON '87*, Volume 1, pages 454–463, November 1987.

- 7) Hanselman, H., "LQG-Control of a Highly Resonant Disc Drive Head Positioning Actuator." *IEEE Transactions on Industrial Electronics*, USA, Volume 35, Number 1, pages 100–104, February 1988.

- 8) Jacquot, R., *Modern Digital Control Systems*, New York, NY: Marcel Dekker, Inc., 1981.

- 9) Katz, P., *Digital Control Using Microprocessors*, Englewood Cliffs, NJ: Prentice-Hall, Inc., 1981.

- 10) Kuo, B.C., *Digital Control Systems*, New York, NY: Holt, Reinholt, and Winston, Inc., 1980.

- 11) Lovrich, A., G. Troullinos, and R. Chirayil, "An All-Digital Automatic Gain Control." *Proceedings of ICASSP 88*, USA, Volume D, page 1734, April 1988.

- 12) Matsui, N. and M. Shigyo, "Brushless DC Motor Control Without Position and Speed Sensors." *IEEE Transactions on Industry Applications*, USA, Volume 28, Number 1, Part 1, pages 120–127, January–February 1992.

- 13) Meshkat, S., and I. Ahmed, "Using DSPs in AC Induction Motor Drives." Control Engineering, February 1988.

- 14) Panahi, I. and R. Restle, "DSPs Redefine Motion Control." *Motion Control Magazine*, December 1993.

- 15) Phillips, C., and H. Nagle, *Digital Control System Analysis and Design*, Englewood Cliffs, NJ: Prentice-Hall, Inc., 1984.

#### Multimedia:

- Reimer, J., "DSP-Based Multimedia Solutions Lead Way Enhancing Audio Compression Performance." Dr. Dobbs Journal, December 1993.

- Reimer, J., G. Benbassat, and W. Bonneau Jr., "Application Processors: Making PC Multimedia Happen." Silicon Valley PC Design Conference, July 1991.

#### Military:

1) Papamichalis, P., and J. Reimer, "Implementation of the Data Encryption Standard Using the TMS32010." *Digital Signal Processing Applications*, 1986.

#### Telecommunications:

- Ahmed, I., and A. Lovrich, "Adaptive Line Enhancer Using the TMS320C25." Conference Records of Northcon/86, USA, 14/3/1–10, September/October 1986.

- Casale, S., R. Russo, and G. Bellina, "Optimal Architectural Solution Using DSP Processors for the Implementation of an ADPCM Transcoder." Proceedings of GLOBECOM '89, pages 1267–1273, November 1989.

- 3) Cole, C., A. Haoui, and P. Winship, "A High-Performance Digital Voice Echo Canceller on a SINGLE TMS32020." *Proceedings of ICASSP 86*, USA, Catalog Number 86CH2243–4, Volume 1, pages 429–432, April 1986.

- 4) Cole, C., A. Haoui, and P. Winship, "A High-Performance Digital Voice Echo Canceller on a Single TMS32020." *Proceedings of IEEE*

- International Conference on Acoustics, Speech and Signal Processing, USA, 1986.

- 5) Lovrich, A., and J. Reimer, "A Multi-Rate Transcoder." *Transactions on Consumer Electronics*, USA, November 1989.

- 6) Lovrich, A. and J. Reimer, "A Multi-Rate Transcoder." *Digest of Technical Papers for 1989 International Conference on Consumer Electronics*, June 7–9, 1989.

- Lu, H., D. Hedberg, and B. Fraenkel, "Implementation of High-Speed Voiceband Data Modems Using the TMS320C25." *Proceedings of ICASSP 87*, USA, Catalog Number 87CH2396–0, Volume 4, pages 1915–1918, April 1987.

- Mock, P., "Add DTMF Generation and Decoding to DSP– μP Designs." *Electronic Design*, USA, Volume 30, Number 6, pages 205–213, March 1985.

- 9) Reimer, J., M. McMahan, and M. Arjmand, "ADPCM on a TMS320 DSP Chip." *Proceedings of SPEECH TECH 85*, pages 246–249, April 1985.

- Troullinos, G., and J. Bradley, "Split-Band Modem Implementation Using the TMS32010 Digital Signal Processor." Conference Records of Electro/86 and Mini/Micro Northeast, USA, 14/1/1–21, May 1986.

#### Automotive:

1) Lin, K., "Trends of Digital Signal Processing in Automotive." *International Congress on Transportation Electronic (CONVERGENCE '88*), October 1988.

#### Consumer:

- 1) Frantz, G.A., J.B. Reimer, and R.A. Wotiz, "Julie, The Application of DSP to a Product." *Speech Tech Magazine*, USA, September 1988.

- Reimer, J.B., and G.A. Frantz, "Customization of a DSP Integrated Circuit for a Customer Product." *Transactions on Consumer Electronics*, USA, August 1988.

- 3) Reimer, J.B., P.E. Nixon, E.B. Boles, and G.A. Frantz, "Audio Customization of a DSP IC." *Digest of Technical Papers for 1988 International Conference on Consumer Electronics*, June 8–10 1988.

#### Medical:

Knapp and Townshend, "A Real-Time Digital Signal Processing System for an Auditory Prosthesis." *Proceedings of ICASSP 88*, USA, Volume A, page 2493, April 1988.  Morris, L.R., and P.B. Barszczewski, "Design and Evolution of a Pocket-Sized DSP Speech Processing System for a Cochlear Implant and Other Hearing Prosthesis Applications." *Proceedings of ICASSP 88*, USA, Volume A, page 2516, April 1988.

#### Development Support:

- Mersereau, R., R. Schafer, T. Barnwell, and D. Smith, "A Digital Filter Design Package for PCs and TMS320." MIDCON/84 Electronic Show and Convention, USA, 1984.

- 2) Simar, Jr., R., and A. Davis, "The Application of High-Level Languages to Single-Chip Digital Signal Processors." *Proceedings of ICASSP 88*, USA, Volume 3, pages 1678–1681, April 1988.

#### If You Need Assistance. . .

| If you want to                                                                                  | Do this                                                                                                                              |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Request more information about<br>Texas Instruments Digital Signal<br>Processing (DSP) products | Write to: Texas Instruments Incorporated Market Communications Manager MS 736 P.O. Box 1443 Houston, Texas 77251–1443                |

| Order Texas Instruments documentation                                                           | Call the TI Literature Response Center: (800) 477–8924                                                                               |

| Ask questions about product operation or report suspected problems                              | Contact the DSP hotline: Phone: (713) 274–2320 FAX: (713) 274–2324 Electronic Mail: 4389750@mcimail.com.                             |

| Obtain the source code in this user's guide.                                                    | Call the TI BBS: (713) 274–2323                                                                                                      |

|                                                                                                 | Ftp from:  ftp.ti.com log in as user ftp cd to /mirrors/tms320bbs                                                                    |

| Visit TI online, including TI&ME™, your own customized web page.                                | Point your browser at: http://www.ti.com                                                                                             |

| Report mistakes or make comments about this or any other TI                                     | Send electronic mail to: comments@books.sc.ti.com                                                                                    |

| documentation.                                                                                  | Send printed comments to: Texas Instruments Incorporated Technical Publications Mgr., MS 702 P.O. Box 1443 Houston, Texas 77251–1443 |

#### **Trademarks**

MS is a registered trademark of Microsoft Corp.

MS-Windows is a registered trademark of Microsoft Corp.

MS-DOS is a registered trademark of Microsoft Corp.

OS/2 is a trademark of International Business Machines Corp.

Sun and SPARC are trademarks of Sun Microsystems, Inc.

VAX and VMS are trademarks of Digital Equipment Corp.

## **Contents**

| 1 |         |          |                                                                               | 1-1  |

|---|---------|----------|-------------------------------------------------------------------------------|------|

|   | Introd  |          | e TMS320 family and the TMS320C4x                                             |      |

|   | 1.1     | TMS3     | 20C4x Devices                                                                 |      |

|   |         | 1.1.1    | The TMS320C40                                                                 |      |

|   |         | 1.1.2    | The TMS320C44                                                                 | 1-2  |

|   | 1.2     | ,        | eatures of the TMS320C4x                                                      |      |

|   | 1.3     | TMS3     | 20C40 and TMS320C44 Device Comparison                                         | 1-4  |

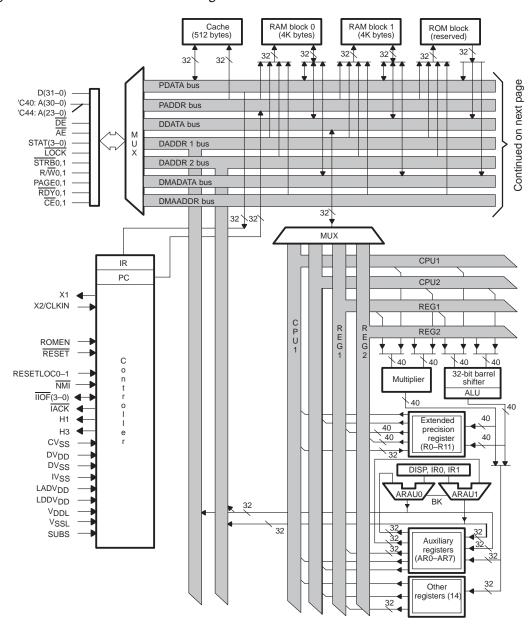

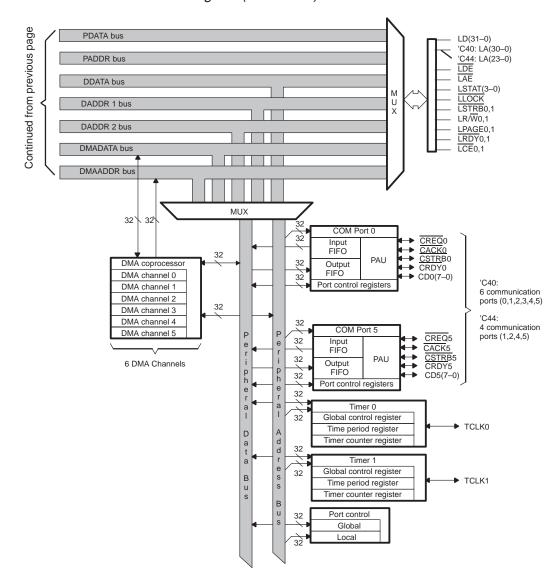

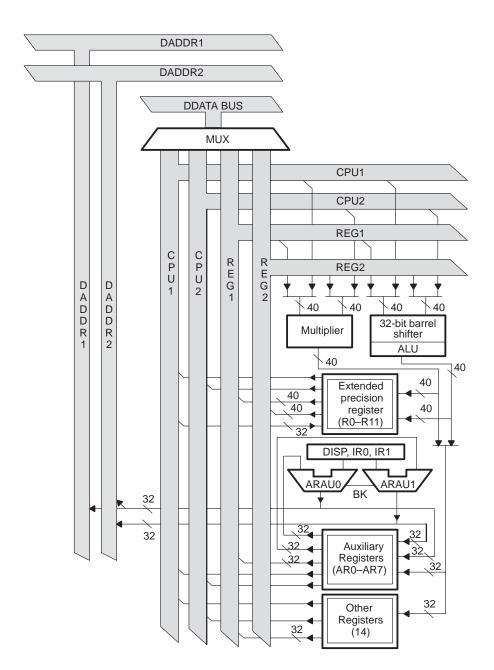

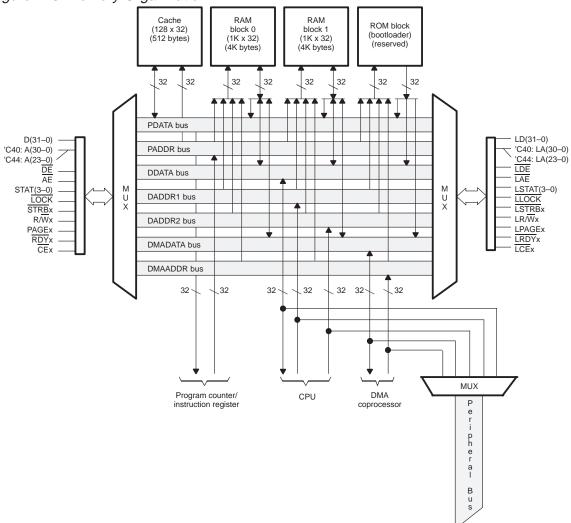

| 2 | Archi   | tectura  | Il Overview                                                                   | 2-1  |

|   | Briefly | y descri | bes the architecture of the CPU, buses, interrupts, and peripherals of the 'C | C4x  |

|   | 2.1     | Centra   | al Processing Unit (CPU)                                                      | 2-4  |

|   |         | 2.1.1    | Floating-Point/Integer Multiplier                                             | 2-4  |

|   |         | 2.1.2    | Arithmetic Logic Unit (ALU) and Internal Buses                                | 2-4  |

|   |         | 2.1.3    | Auxiliary Register Arithmetic Units (ARAUs)                                   | 2-6  |

|   |         | 2.1.4    | CPU Primary Register File                                                     |      |

|   |         | 2.1.5    | CPU Expansion Register File                                                   | 2-10 |

|   | 2.2     | Memo     | ry Organization                                                               |      |

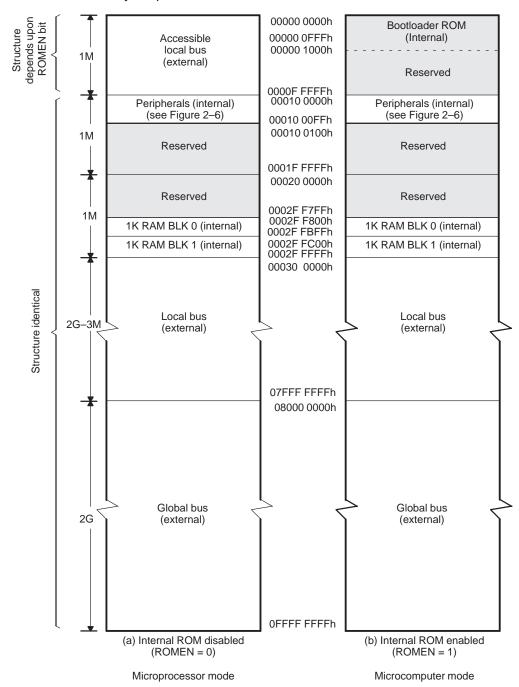

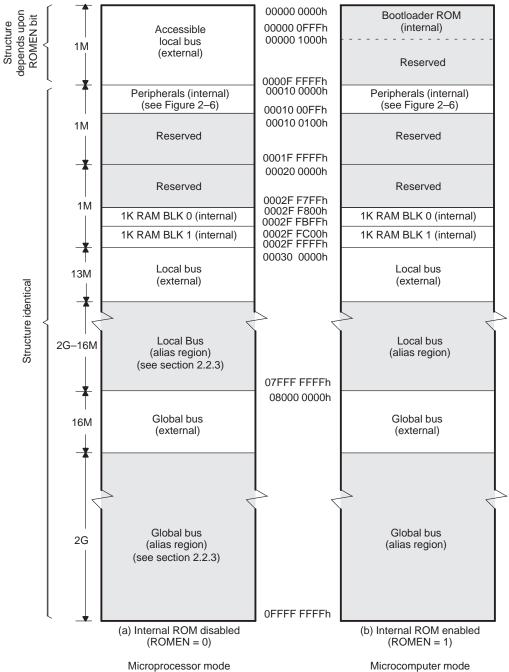

|   |         | 2.2.1    | RAM, ROM, and Cache                                                           | 2-11 |

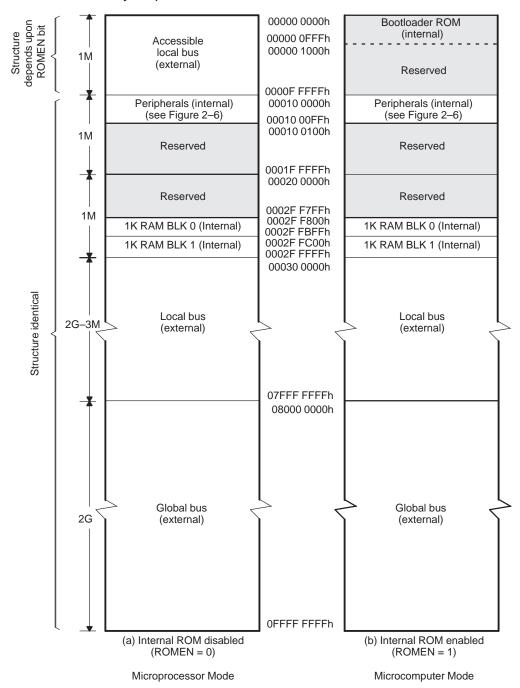

|   |         | 2.2.2    | Memory Maps                                                                   |      |

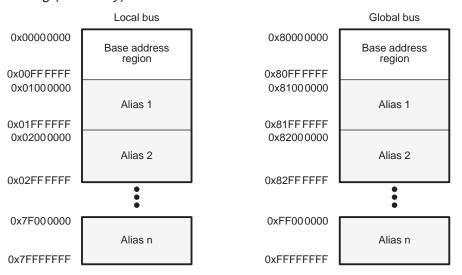

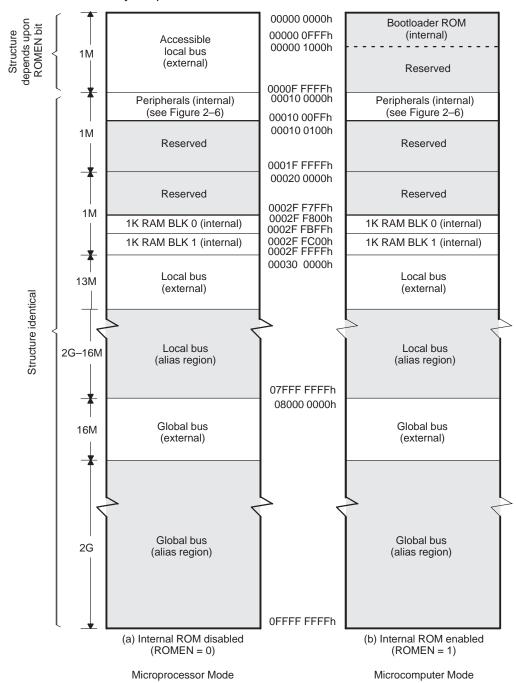

|   |         | 2.2.3    | Memory Aliasing ('C44 only)                                                   | 2-17 |

|   |         | 2.2.4    | Memory Addressing Modes                                                       | 2-18 |

|   | 2.3     | Interna  | al Bus Operation                                                              | 2-19 |

|   | 2.4     | Extern   | al Bus Operation                                                              | 2-20 |

|   | 2.5     |          | pts                                                                           |      |

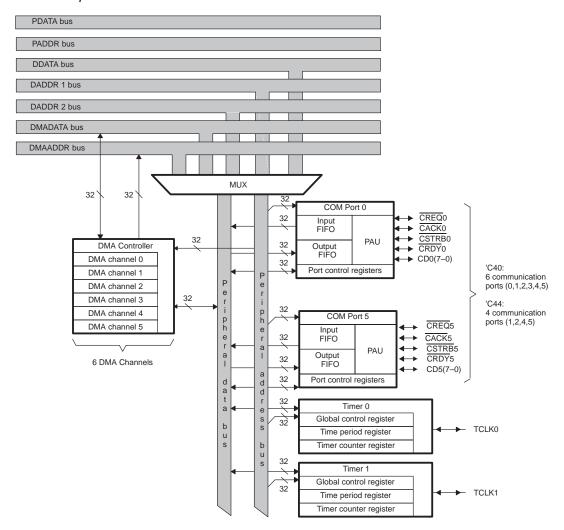

|   | 2.6     |          | erals                                                                         |      |

|   |         | 2.6.1    | Communication Ports                                                           |      |

|   |         | 2.6.2    | Direct Memory Access (DMA) Coprocessor                                        |      |

|   |         |          | , , ,                                                                         |      |

| 3 | Lists | _              | rs cribes the contents of the CPU primary register file and the CPU expansion                                    |           |

|---|-------|----------------|------------------------------------------------------------------------------------------------------------------|-----------|

|   | 3.1   | CPU P          | rimary Register File                                                                                             | . 3-2     |

|   |       | 3.1.1          | Extended-Precision Registers (R0–R11)                                                                            |           |

|   |       | 3.1.2          | Auxiliary Registers (AR0–AR7)                                                                                    |           |

|   |       | 3.1.3          | Data-Page Pointer (DP)                                                                                           | . 3-4     |

|   |       | 3.1.4          | Index Registers (IR0, IR1)                                                                                       | . 3-4     |

|   |       | 3.1.5          | Block-Size Register (BK)                                                                                         |           |

|   |       | 3.1.6          | System Stack Pointer (SP)                                                                                        |           |

|   |       | 3.1.7          | Status Register (ST)                                                                                             |           |

|   |       | 3.1.8          | DMA Coprocessor Interrupt Enable Register (DIE)                                                                  |           |

|   |       | 3.1.9          | CPU Internal Interrupt Enable Register (IIE)                                                                     |           |

|   |       | 3.1.10         | IIOF Flag Register (IIF)                                                                                         |           |

|   |       | 3.1.11         | Block-Repeat (RS, RE) and Repeat-Count (RC) Registers                                                            |           |

|   |       | 3.1.12         | • ' '                                                                                                            |           |

|   | 3.2   |                | Reserved Bits and Compatibilityxpansion Register File                                                            |           |

|   | 3.2   | CPU E          | xpansion Register File                                                                                           | 3-17      |

| 4 |       | -              | the Instruction Cache                                                                                            | . 4-1     |

|   | 4.1   | Memor          | y Map                                                                                                            | . 4-2     |

|   | 4.2   |                | eral Bus Memory Map                                                                                              |           |

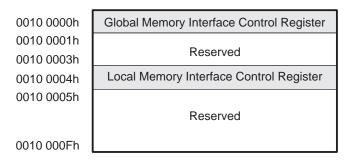

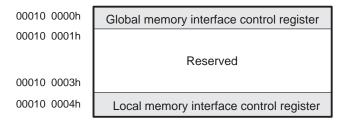

|   |       | 4.2.1          | Local and Global Memory Interface Control Registers                                                              | . 4-6     |

|   |       | 4.2.2          | Analysis Module Registers                                                                                        | . 4-6     |

|   |       | 4.2.3          | Timer Registers                                                                                                  | . 4-7     |

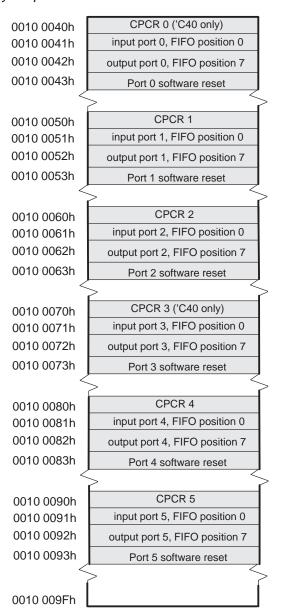

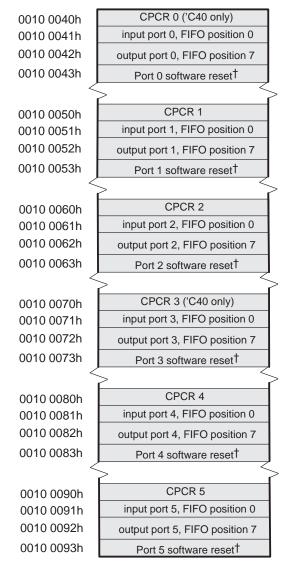

|   |       | 4.2.4          | Communication Port Memory Map                                                                                    |           |

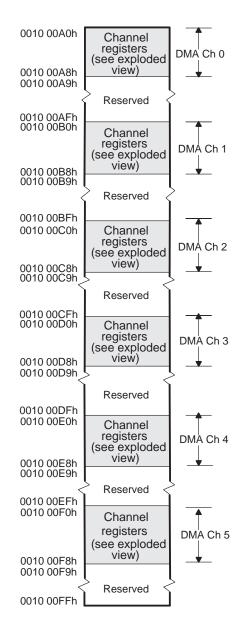

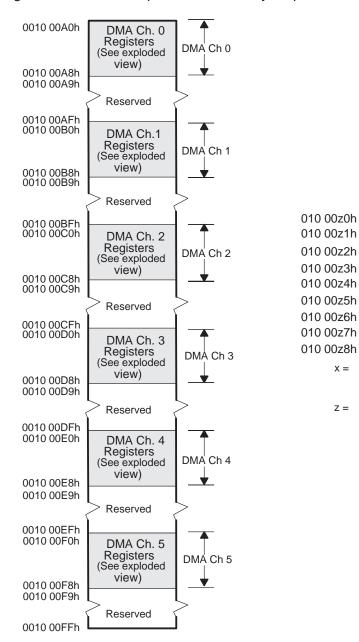

|   |       | 4.2.5          | DMA Coprocessor Registers                                                                                        |           |

|   | 4.3   |                | tion Cache                                                                                                       |           |

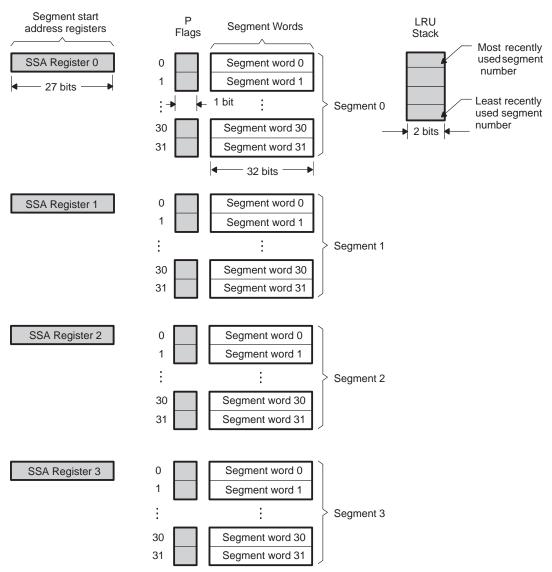

|   |       | 4.3.1          | Instruction Cache Architecture                                                                                   |           |

|   |       | 4.3.2          | Cache Control Bits                                                                                               |           |

|   |       | 4.3.3<br>4.3.4 | Using the Cache                                                                                                  |           |

|   |       | 4.3.4          | The LRU Cache Algorithm                                                                                          | 4-14      |

| 5 | Data  | Formats        | s and Floating-Point Operation                                                                                   | . 5-1     |

|   |       |                | eger and floating-point data formats and discusses how some mathematica<br>e performed on floating-point numbers | <i>al</i> |

|   | 5.1   | Signed         | -Integer Formats                                                                                                 | . 5-2     |

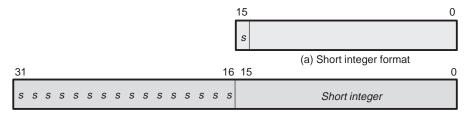

|   |       | 5.1.1          | Short Integer Format                                                                                             | . 5-2     |

|   |       | 5.1.2          | Single-Precision Integer Format                                                                                  |           |

|   | 5.2   | Unsign         | ed-Integer Formats                                                                                               |           |

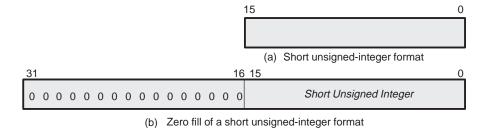

|   |       | 5.2.1          | Short Unsigned-Integer Format                                                                                    |           |

|   |       | 5.2.2          | Single-Precision Unsigned-Integer Format                                                                         | . 5-3     |

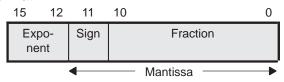

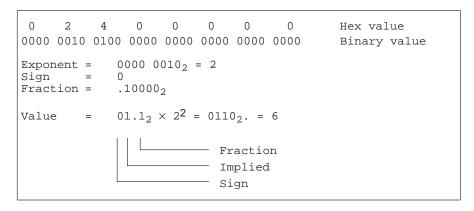

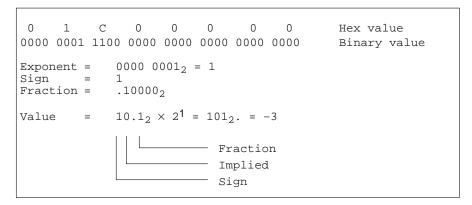

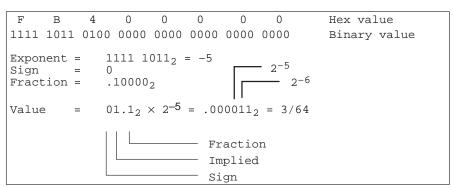

|   | 5.3   | Floating-Point Formats                                                             | . 5-4 |

|---|-------|------------------------------------------------------------------------------------|-------|

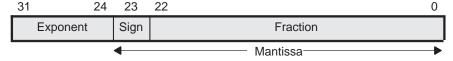

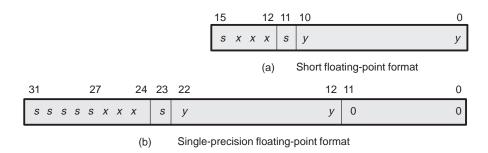

|   |       | 5.3.1 Short Floating-Point Format                                                  | . 5-5 |

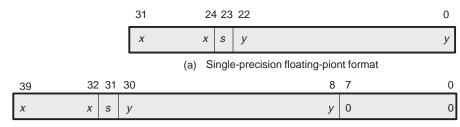

|   |       | 5.3.2 Single-Precision Floating-Point Format                                       | . 5-6 |

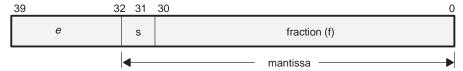

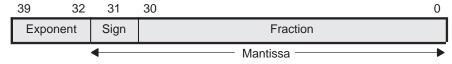

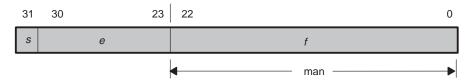

|   |       | 5.3.3 Extended-Precision Floating-Point Format                                     | . 5-7 |

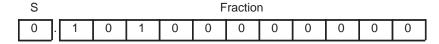

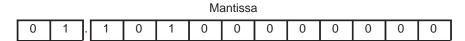

|   |       | 5.3.4 Determining the Decimal Equivalent of a Floating-Point Number                | . 5-8 |

|   |       | 5.3.5 Conversion Between Floating-Point Formats                                    | 5-11  |

|   | 5.4   | Floating-Point Conversion (IEEE Std. 754)                                          | 5-13  |

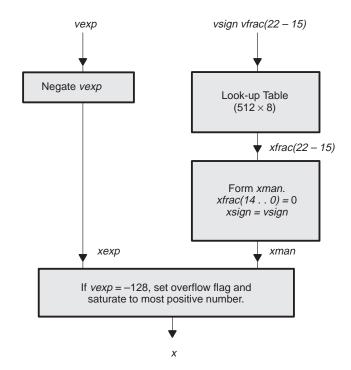

|   |       | 5.4.1 Converting IEEE Format to Twos-Complement 'C4x Floating-Point Format .       | 5-14  |

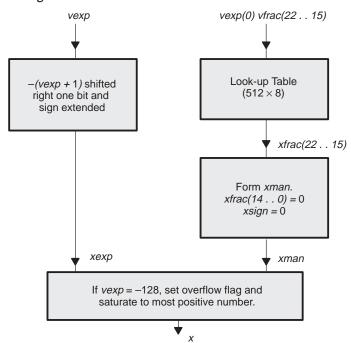

|   |       | 5.4.2 Converting Twos-Complement 'C4x Floating-Point Format to IEEE Format .       | 5-17  |

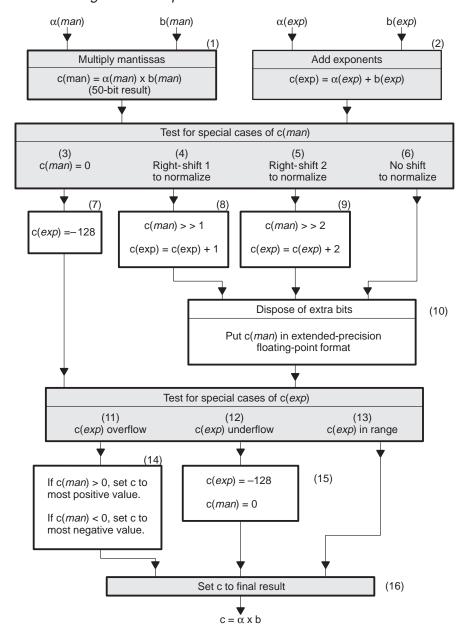

|   | 5.5   | Floating-Point Multiplication                                                      | 5-19  |

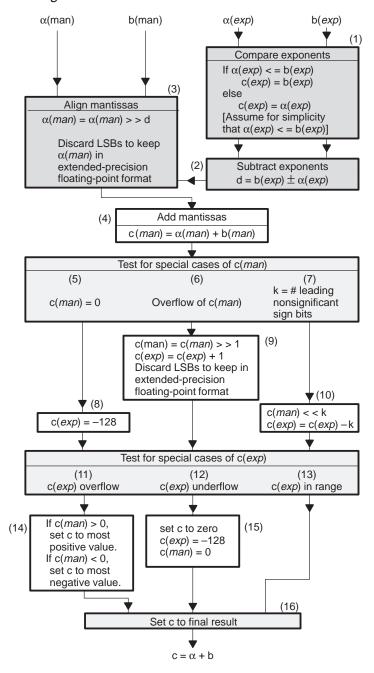

|   | 5.6   | Floating-Point Addition and Subtraction                                            | 5-23  |

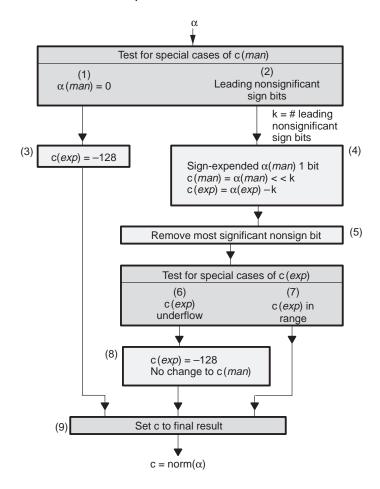

|   | 5.7   | Normalization (NORM Instruction)                                                   | 5-27  |

|   | 5.8   | Rounding (RND Instruction)                                                         | 5-29  |

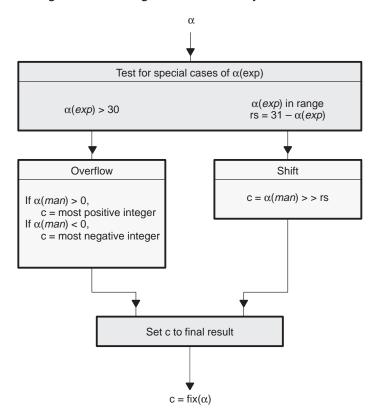

|   | 5.9   | Floating-Point-to-Integer Conversion (FIX Instruction)                             | 5-31  |

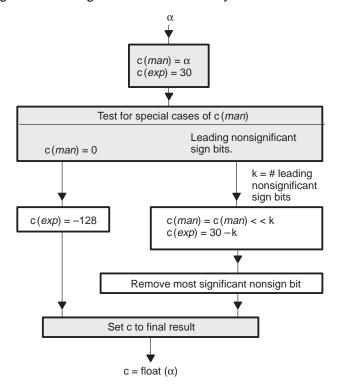

|   | 5.10  | Integer-to-Floating-Point Conversion (FLOAT Instruction)                           | 5-33  |

|   | 5.11  | Reciprocal (RCPF Instruction)                                                      | 5-34  |

|   |       | 5.11.1 Reciprocal Algorithm                                                        | 5-35  |

|   | 5.12  | Reciprocal Square Root (RSQRF Instruction)                                         |       |

|   |       | Newton-Raphson Algorithm                                                           | 5-37  |

| 6 | Addr  | essing Modes                                                                       | . 6-1 |

|   | Desci | ribes addressing modes, using address registers, and stack managements in the 'C4x | (     |

|   | 6.1   | Addressing Types                                                                   | . 6-2 |

|   | 6.2   | Register Addressing                                                                |       |

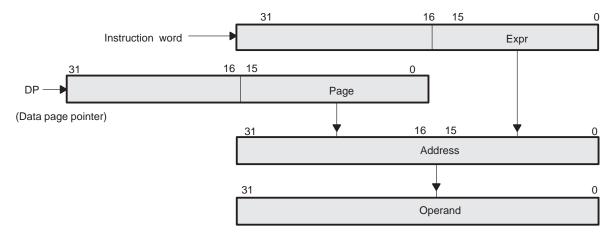

|   | 6.3   | Direct Addressing                                                                  |       |

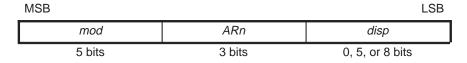

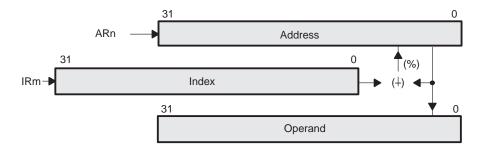

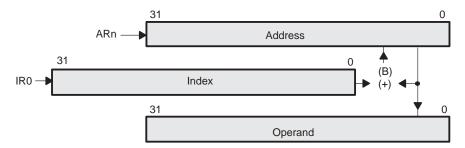

|   | 6.4   | Indirect Addressing                                                                |       |

|   | 6.5   | Immediate Addressing                                                               |       |

|   | 6.6   | PC-Relative Addressing                                                             |       |

|   | 6.7   | Encoding of Addressing Modes                                                       |       |

|   |       | 6.7.1 General Addressing Modes                                                     |       |

|   |       | 6.7.2 Three-Operand Addressing Modes                                               | 6-22  |

|   |       | 6.7.3 Parallel Addressing Modes                                                    | 6-24  |

|   |       | 6.7.4 Conditional-Branch Addressing Modes                                          | 6-25  |

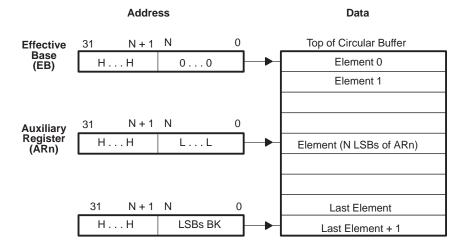

|   | 6.8   | Circular Addressing                                                                | 6-27  |

|   | 6.9   | Bit-Reversed Addressing                                                            | 6-32  |

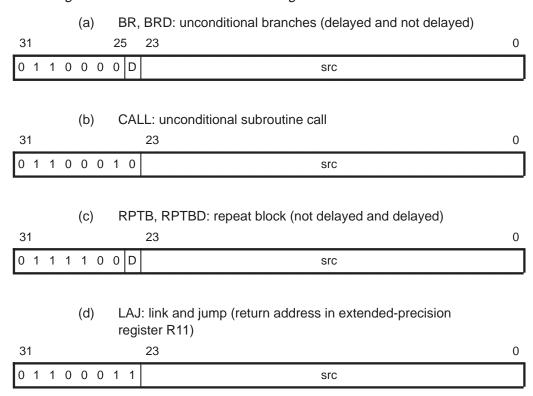

| 7 | Progi | ram Flow Control                                                                   | . 7-1 |

|   | Desci | ribes software and hardware features that control how a program flows              |       |

|   | 7.1   | Repeat Mode                                                                        |       |

|   |       | 7.1.1 Control Bits                                                                 |       |

|   |       | 7.1.2 Repeat-Mode Operation                                                        |       |

|   |       | 7.1.3 RPTB and RPTBD Instructions                                                  |       |

|   |       | 7.1.4 RPTS Instruction                                                             |       |

|   |       | 7.1.5 Repeat Mode Restriction Rules                                                |       |

|   |       | 7.1.6 RC Register Value After Repeat Mode Completes                                |       |

|   |       | 7.1.7 Nesting Block Repeats                                                        |       |

|   |       |                                                                                    |       |

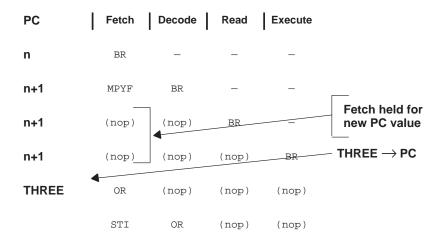

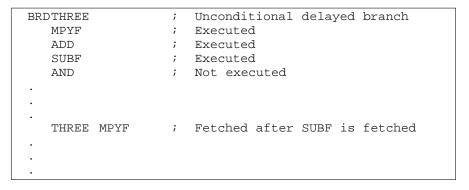

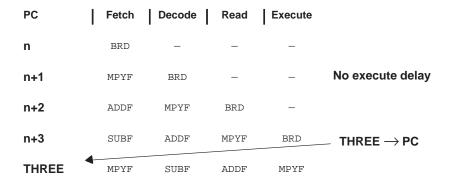

|   | 7.2                                                      | Delaye                                                                                                      | d Branches                                                                                                                                                                                                                                                                                                                             |                                           |

|---|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|   |                                                          | 7.2.1                                                                                                       | Delayed Branches Without Annulling                                                                                                                                                                                                                                                                                                     |                                           |

|   |                                                          | 7.2.2                                                                                                       | Delayed Branches With Annulling                                                                                                                                                                                                                                                                                                        | 7-11                                      |

|   | 7.3                                                      | Calls, T                                                                                                    | Fraps, Branches, Jumps, and Returns                                                                                                                                                                                                                                                                                                    | 7-12                                      |

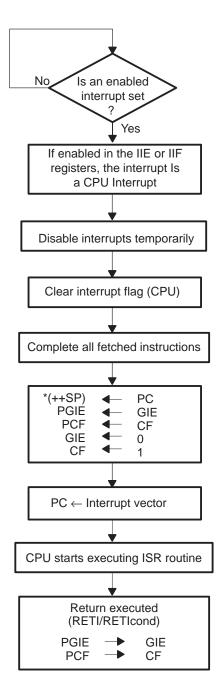

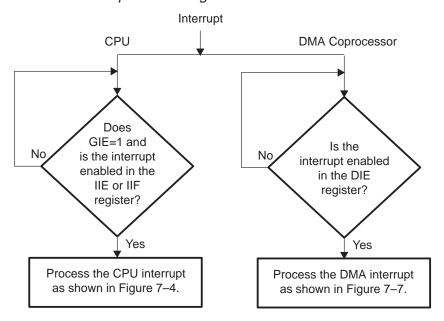

|   | 7.4                                                      | Interrup                                                                                                    | ots                                                                                                                                                                                                                                                                                                                                    | 7-15                                      |

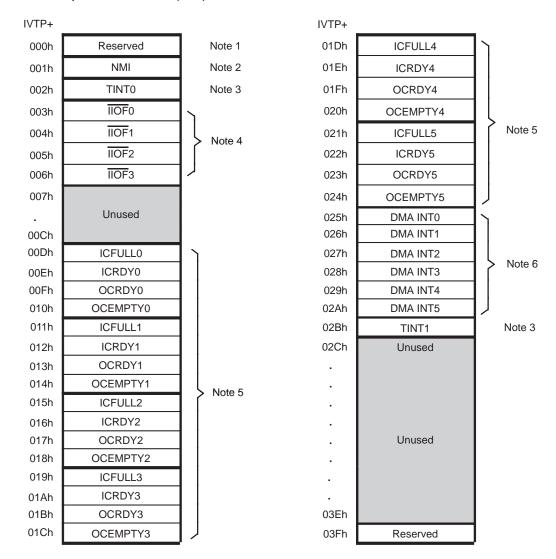

|   |                                                          | 7.4.1                                                                                                       | Interrupt Vector Table and Prioritization                                                                                                                                                                                                                                                                                              | 7-15                                      |

|   |                                                          | 7.4.2                                                                                                       | CPU Interrupt Control Bits                                                                                                                                                                                                                                                                                                             | 7-17                                      |

|   |                                                          | 7.4.3                                                                                                       | Interrupt Processing                                                                                                                                                                                                                                                                                                                   | 7-18                                      |

|   |                                                          | 7.4.4                                                                                                       | CPU Interrupt Latency                                                                                                                                                                                                                                                                                                                  | 7-20                                      |

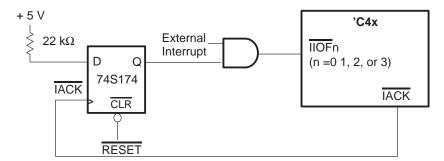

|   |                                                          | 7.4.5                                                                                                       | External Interrupts                                                                                                                                                                                                                                                                                                                    | 7-21                                      |

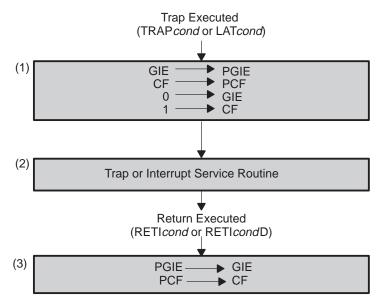

|   | 7.5                                                      | Traps                                                                                                       |                                                                                                                                                                                                                                                                                                                                        | 7-24                                      |

|   |                                                          | 7.5.1                                                                                                       | Initialization of Traps and Interrupts                                                                                                                                                                                                                                                                                                 | 7-24                                      |

|   |                                                          | 7.5.2                                                                                                       | Operation of Traps                                                                                                                                                                                                                                                                                                                     | 7-24                                      |

|   |                                                          | 7.5.3                                                                                                       | Overlapping the Trap and Interrupt Vector Tables                                                                                                                                                                                                                                                                                       | 7-25                                      |

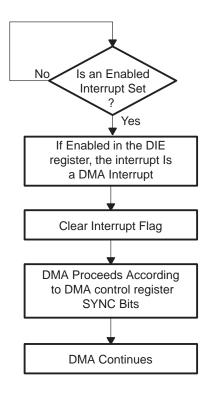

|   | 7.6                                                      | DMA In                                                                                                      | iterrupts                                                                                                                                                                                                                                                                                                                              | 7-26                                      |

|   |                                                          | 7.6.1                                                                                                       | DMA Interrupt Control Bits                                                                                                                                                                                                                                                                                                             | 7-26                                      |

|   |                                                          | 7.6.2                                                                                                       | DMA Interrupt Processing                                                                                                                                                                                                                                                                                                               | 7-27                                      |

|   |                                                          | 7.6.3                                                                                                       | CPU/DMA Interrupt Interaction                                                                                                                                                                                                                                                                                                          | 7-28                                      |

|   | 7.7                                                      | Reset                                                                                                       |                                                                                                                                                                                                                                                                                                                                        | 7-29                                      |

|   |                                                          | 7.7.1                                                                                                       | Reset's Effects on Pin States                                                                                                                                                                                                                                                                                                          | 7-29                                      |

|   |                                                          | 7.7.2                                                                                                       | Reset Vector Location                                                                                                                                                                                                                                                                                                                  | 7-35                                      |

|   |                                                          | 7.7.3                                                                                                       | Additional Reset Operations                                                                                                                                                                                                                                                                                                            | 7-35                                      |

| 8 | Pinel                                                    | ine Onei                                                                                                    | ration                                                                                                                                                                                                                                                                                                                                 | 8-1                                       |

| • |                                                          | •                                                                                                           | d explains the operation of the four pipeline stages in the 'C4x CPU                                                                                                                                                                                                                                                                   |                                           |

|   |                                                          | indee and                                                                                                   |                                                                                                                                                                                                                                                                                                                                        |                                           |

|   |                                                          | Dinalina                                                                                                    | a Christiana                                                                                                                                                                                                                                                                                                                           | 0.0                                       |

|   | 8.1                                                      |                                                                                                             | e Structure                                                                                                                                                                                                                                                                                                                            |                                           |

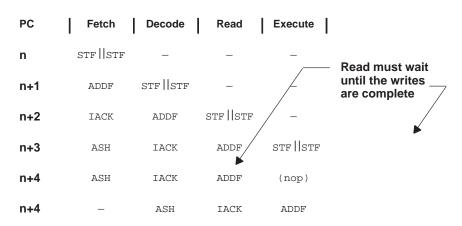

|   | 8.2                                                      | Pipeline                                                                                                    | e Conflicts                                                                                                                                                                                                                                                                                                                            | 8-4                                       |

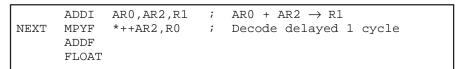

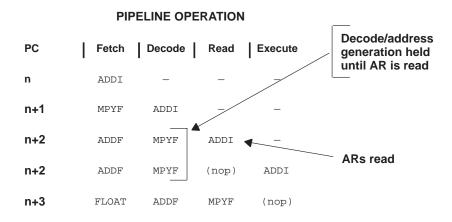

|   |                                                          | Pipeline<br>8.2.1                                                                                           | e Conflicts                                                                                                                                                                                                                                                                                                                            | 8-4<br>8-4                                |

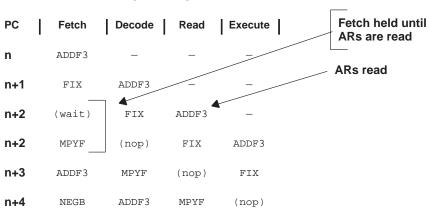

|   |                                                          | Pipeline<br>8.2.1<br>8.2.2                                                                                  | e Conflicts Branch Conflicts Register Conflicts                                                                                                                                                                                                                                                                                        | 8-4<br>8-4<br>8-8                         |

|   | 8.2                                                      | Pipeline<br>8.2.1<br>8.2.2<br>8.2.3                                                                         | e Conflicts Branch Conflicts Register Conflicts Memory Conflicts                                                                                                                                                                                                                                                                       | 8-4<br>8-4<br>8-8                         |

|   | 8.2                                                      | Pipeline<br>8.2.1<br>8.2.2<br>8.2.3<br>Memory                                                               | e Conflicts Branch Conflicts Register Conflicts Memory Conflicts y Accesses for Maximum Performance                                                                                                                                                                                                                                    | 8-4<br>8-4<br>8-8<br>8-10                 |

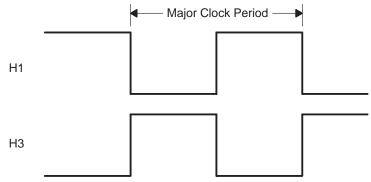

|   | 8.2                                                      | Pipeline<br>8.2.1<br>8.2.2<br>8.2.3<br>Memory<br>Clockin                                                    | e Conflicts Branch Conflicts Register Conflicts Memory Conflicts y Accesses for Maximum Performance g of Memory Accesses                                                                                                                                                                                                               | 8-4<br>8-4<br>8-8<br>8-10<br>8-17         |

|   | 8.2                                                      | Pipeline<br>8.2.1<br>8.2.2<br>8.2.3<br>Memory<br>Clockin<br>8.4.1                                           | e Conflicts Branch Conflicts Register Conflicts Memory Conflicts y Accesses for Maximum Performance og of Memory Accesses Program Fetches                                                                                                                                                                                              | 8-4<br>8-4<br>8-8<br>8-10<br>8-17<br>8-19 |

|   | 8.2                                                      | Pipeline<br>8.2.1<br>8.2.2<br>8.2.3<br>Memory<br>Clockin                                                    | e Conflicts Branch Conflicts Register Conflicts Memory Conflicts y Accesses for Maximum Performance g of Memory Accesses                                                                                                                                                                                                               | 8-4<br>8-4<br>8-8<br>8-10<br>8-17<br>8-19 |

| 9 | 8.2<br>8.3<br>8.4                                        | Pipeline<br>8.2.1<br>8.2.2<br>8.2.3<br>Memory<br>Clockin<br>8.4.1<br>8.4.2                                  | e Conflicts Branch Conflicts Register Conflicts Memory Conflicts y Accesses for Maximum Performance of of Memory Accesses Program Fetches Data Loads and Stores                                                                                                                                                                        | 8-4<br>8-4<br>8-8<br>8-10<br>8-17<br>8-19 |

| 9 | 8.2<br>8.3<br>8.4                                        | Pipeline<br>8.2.1<br>8.2.2<br>8.2.3<br>Memory<br>Clockin<br>8.4.1<br>8.4.2                                  | e Conflicts Branch Conflicts Register Conflicts Memory Conflicts y Accesses for Maximum Performance og of Memory Accesses Program Fetches                                                                                                                                                                                              | 8-48-48-88-108-178-198-20                 |

| 9 | 8.2<br>8.3<br>8.4                                        | Pipeline<br>8.2.1<br>8.2.2<br>8.2.3<br>Memory<br>Clockin<br>8.4.1<br>8.4.2<br>rnal Bus                      | Branch Conflicts Register Conflicts Memory Conflicts  y Accesses for Maximum Performance og of Memory Accesses Program Fetches Data Loads and Stores  Operation  features and functions of the two 'C4x external buses                                                                                                                 | 8-48-88-108-198-198-20                    |

| 9 | 8.2<br>8.3<br>8.4<br>Exter                               | Pipeline 8.2.1 8.2.2 8.2.3 Memory Clockin 8.4.1 8.4.2 rnal Bus ribes the Overvie                            | e Conflicts Branch Conflicts Register Conflicts Memory Conflicts y Accesses for Maximum Performance og of Memory Accesses Program Fetches Data Loads and Stores  Operation                                                                                                                                                             | 8-48-48-88-108-198-209-1                  |

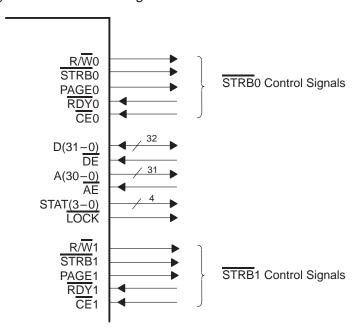

| 9 | 8.2<br>8.3<br>8.4<br>Exter<br>Desc.<br>9.1               | Pipeline 8.2.1 8.2.2 8.2.3 Memory Clockin 8.4.1 8.4.2 rnal Bus ribes the Overvie Memory                     | e Conflicts Branch Conflicts Register Conflicts Memory Conflicts y Accesses for Maximum Performance og of Memory Accesses Program Fetches Data Loads and Stores  Operation features and functions of the two 'C4x external buses ew y Interface Signals                                                                                | 8-48-48-88-108-198-209-1                  |

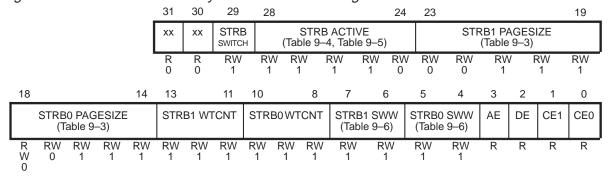

| 9 | 8.2<br>8.3<br>8.4<br>Exter<br>Desc.<br>9.1<br>9.2        | Pipeline 8.2.1 8.2.2 8.2.3 Memory Clockin 8.4.1 8.4.2 rnal Bus ribes the Overvie Memory                     | e Conflicts Branch Conflicts Register Conflicts Memory Conflicts y Accesses for Maximum Performance og of Memory Accesses Program Fetches Data Loads and Stores  Operation features and functions of the two 'C4x external buses ew y Interface Signals y-Interface Control Registers                                                  | 8-48-48-88-178-198-209-1                  |

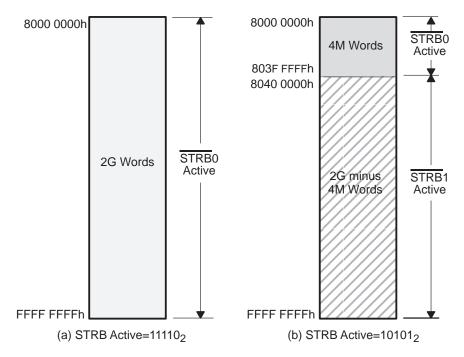

| 9 | 8.2<br>8.3<br>8.4<br>Exter<br>Desc.<br>9.1<br>9.2        | Pipeline 8.2.1 8.2.2 8.2.3 Memory Clockin 8.4.1 8.4.2  rnal Bus ribes the Overvie Memory Memory             | Branch Conflicts Register Conflicts Memory Conflicts  y Accesses for Maximum Performance og of Memory Accesses Program Fetches Data Loads and Stores  Operation  features and functions of the two 'C4x external buses  w  y Interface Signals y-Interface Control Registers Mapping Addresses to Strobes                              | 8-48-48-108-178-198-209-19-29-69-12       |

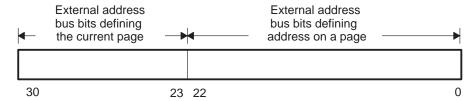

| 9 | 8.2<br>8.3<br>8.4<br>Exter<br>Desc.<br>9.1<br>9.2        | Pipeline 8.2.1 8.2.2 8.2.3 Memory Clockin 8.4.1 8.4.2 rnal Bus ribes the Overvie Memory 9.3.1 9.3.2         | e Conflicts Branch Conflicts Register Conflicts Memory Conflicts y Accesses for Maximum Performance of of Memory Accesses Program Fetches Data Loads and Stores  Operation features and functions of the two 'C4x external buses ew y Interface Signals y-Interface Control Registers Mapping Addresses to Strobes Page Size Operation | 8-48-48-88-108-198-209-19-29-39-129-13    |

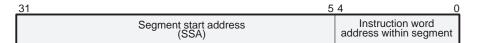

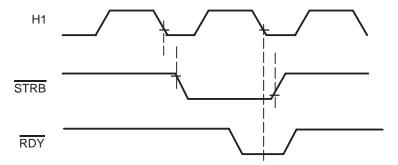

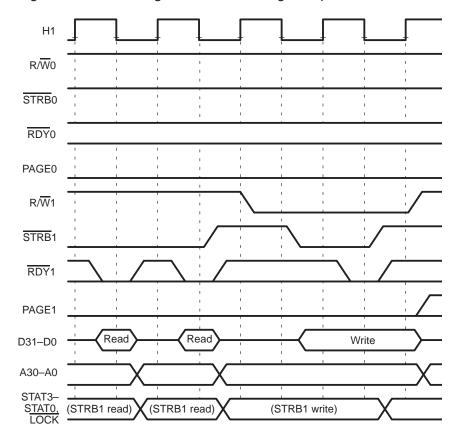

| 9 | 8.2<br>8.3<br>8.4<br>Exter<br>Desc.<br>9.1<br>9.2<br>9.3 | Pipeline 8.2.1 8.2.2 8.2.3 Memory Clockin 8.4.1 8.4.2 rnal Bus ribes the Overvie Memory 9.3.1 9.3.2 Prograr | Branch Conflicts Register Conflicts Memory Conflicts  y Accesses for Maximum Performance og of Memory Accesses Program Fetches Data Loads and Stores  Operation  features and functions of the two 'C4x external buses  w  y Interface Signals y-Interface Control Registers Mapping Addresses to Strobes                              | 8-48-48-108-198-198-209-19-19-129-139-14  |

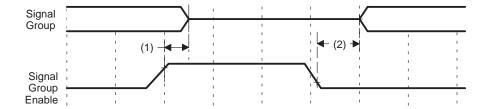

|    | <ul><li>9.6 Using Enable Signals to Control Signal Groups</li></ul> |           |                                                            |       |

|----|---------------------------------------------------------------------|-----------|------------------------------------------------------------|-------|

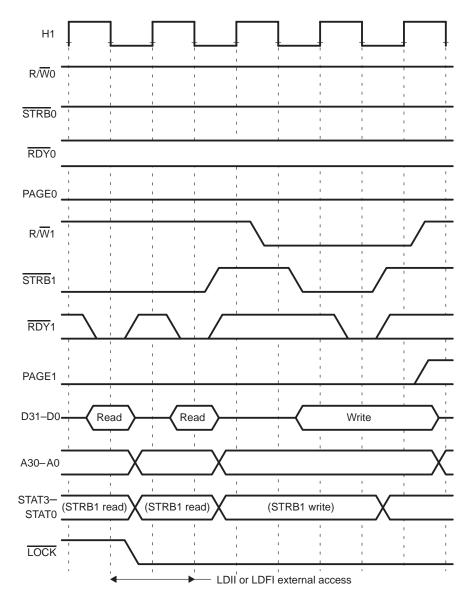

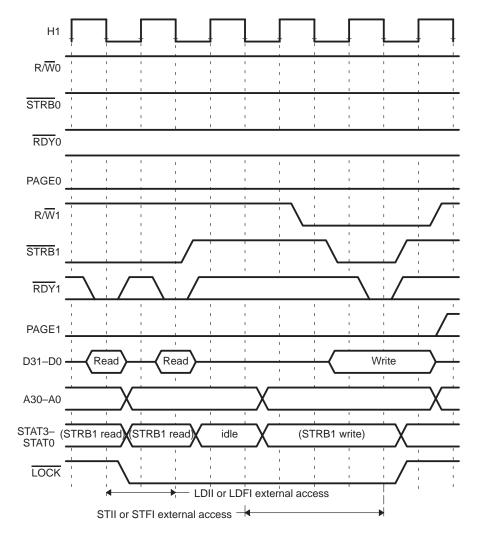

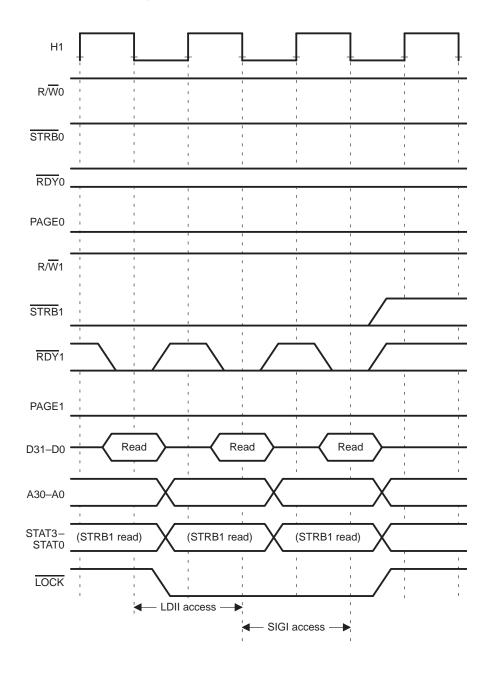

|    | 5.7                                                                 | 9.7.1     | LDFI and LDII                                              |       |

|    |                                                                     | 9.7.2     | STFI and STII                                              |       |

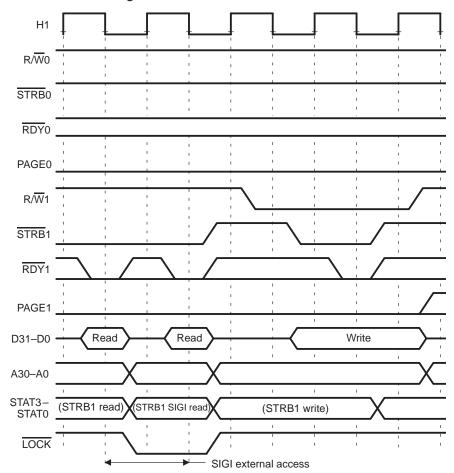

|    |                                                                     | 9.7.3     | SIGI                                                       |       |

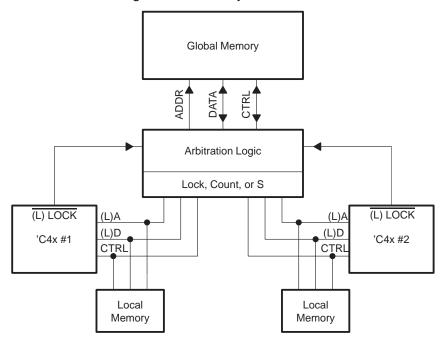

|    |                                                                     | 9.7.4     | Interlocked Examples                                       |       |

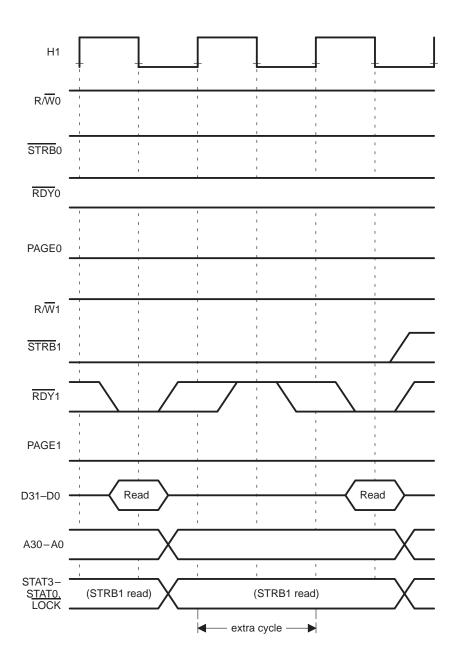

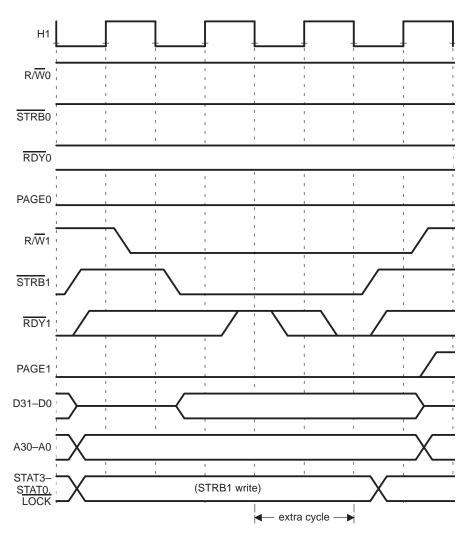

|    |                                                                     | 9.7.5     | Bus-Lock Pins and Bus Timing                               |       |

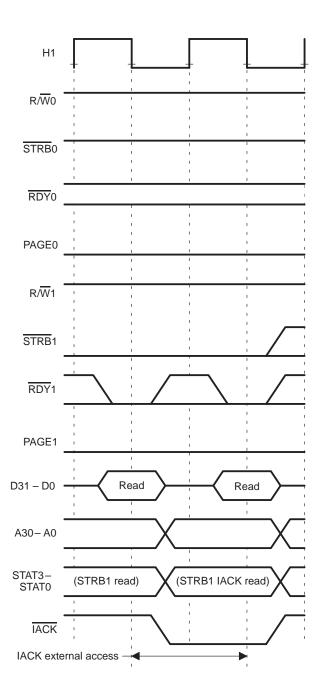

|    | 9.8                                                                 |           | Timing                                                     |       |

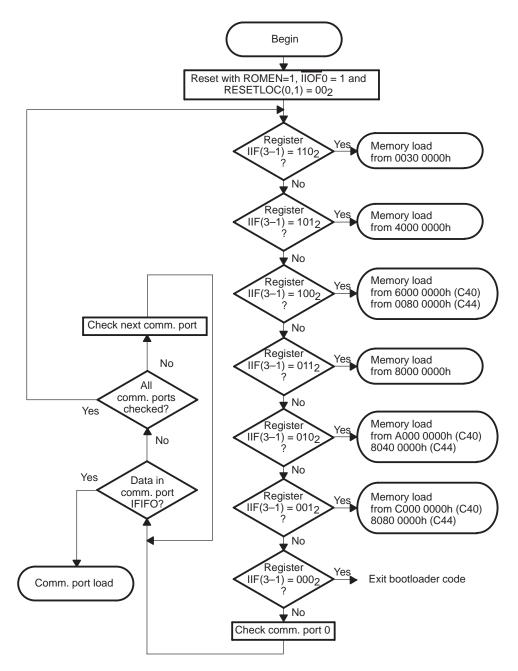

| 10 | The E                                                               | Bootload  | der                                                        | 10-1  |

|    | Desci                                                               | ribes 'C4 | 1x bootloader operation and also lists the bootloader code |       |

|    | 10.1                                                                | Bootloa   | ader Description                                           | 10-2  |

|    | 10.2                                                                | Mode S    | Selection                                                  | 10-3  |

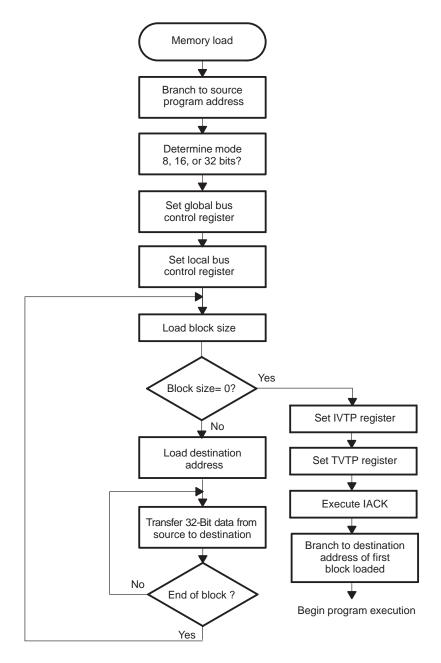

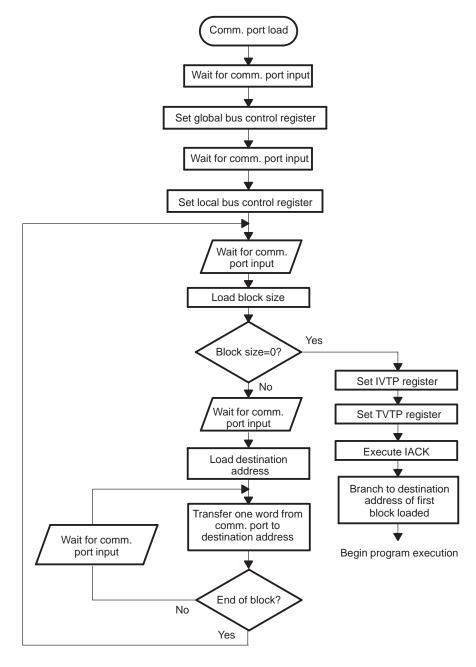

|    | 10.3                                                                | Bootloa   | ading Sequence                                             | 10-5  |

|    | 10.4                                                                | Bootloa   | ading from External Memory (Examples)                      | 10-10 |

|    | 10.5                                                                | Bootloa   | ading from a Communication Port (Examples)                 | 10-16 |

|    | 10.6                                                                | Modifyi   | ing the IIOFx Pins After Bootloading                       | 10-19 |

|    | 10.7                                                                | The Bo    | ootloader Program                                          | 10-20 |

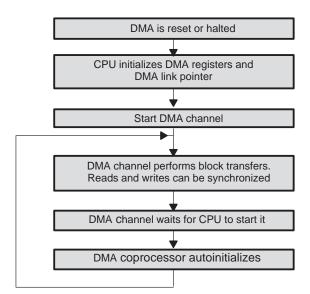

| 11 | The D                                                               | MA Co     | processor                                                  | 11-1  |

|    | Desci                                                               | ribes and | d discusses operation of the 'C4x DMA coprocessor          |       |

|    | 11.1                                                                |           | ction                                                      |       |

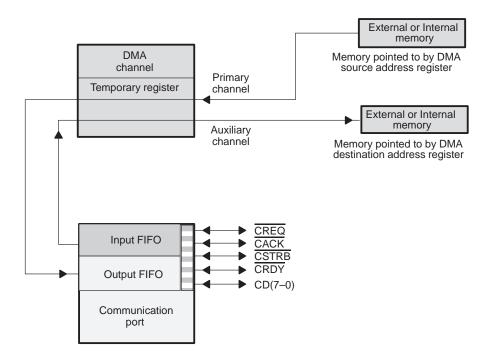

|    | 11.2                                                                |           | unctional Description                                      |       |

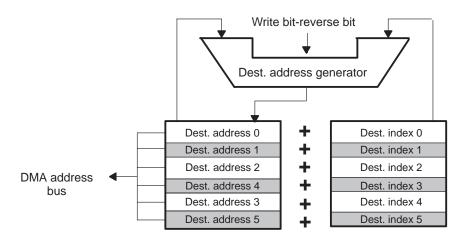

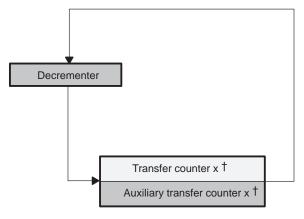

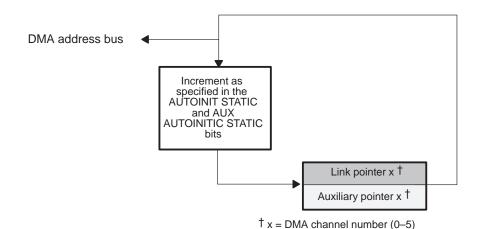

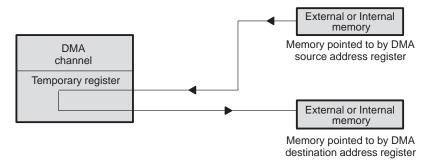

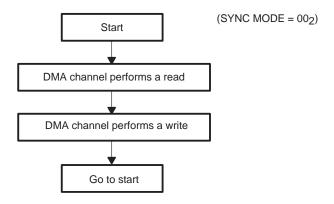

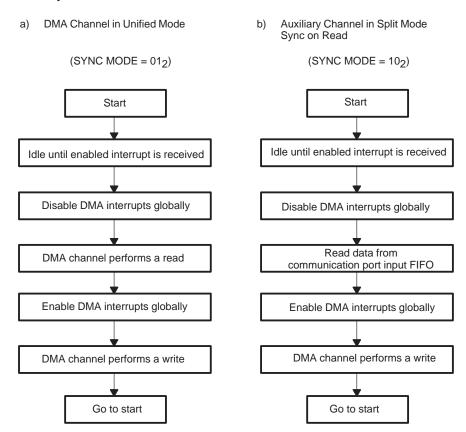

|    |                                                                     |           | DMA Basic Operation                                        |       |

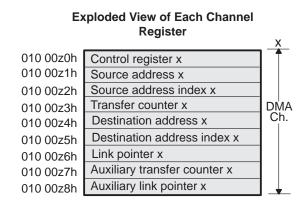

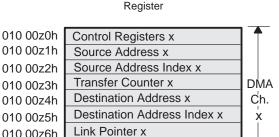

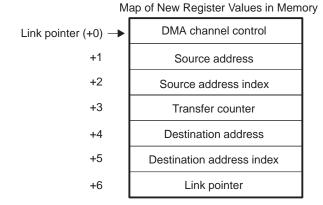

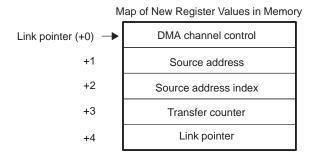

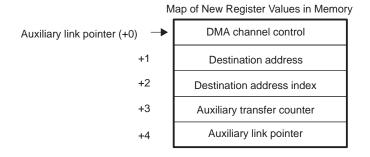

|    | 11.3                                                                |           | Registers                                                  |       |

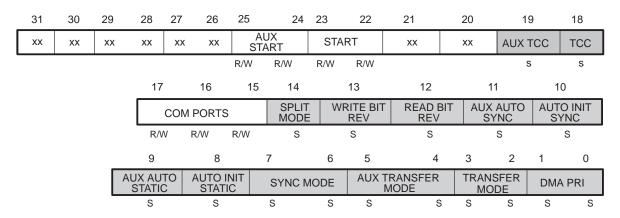

|    |                                                                     |           | Control Register                                           |       |

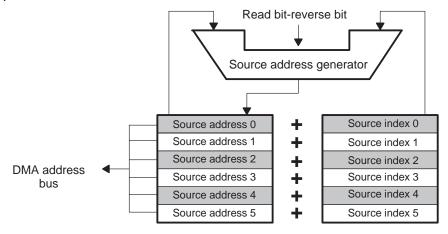

|    |                                                                     | 11.3.2    |                                                            |       |

|    |                                                                     | 11.3.3    | ,,                                                         |       |

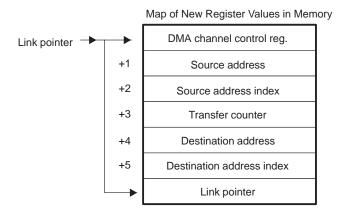

|    |                                                                     |           | Link Pointer and Auxiliary Link-Pointer Registers          |       |

|    | 11.4                                                                |           | Inified Mode                                               |       |

|    | 11.5                                                                |           | Split Mode                                                 |       |

|    | 11.6                                                                |           | nternal Priority Schemes                                   |       |

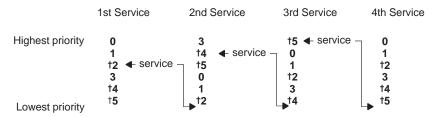

|    |                                                                     |           | Fixed Priority Scheme                                      |       |

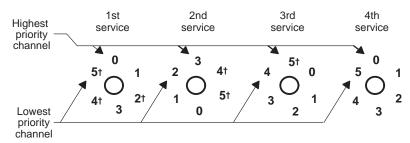

|    |                                                                     | 11.6.2    |                                                            |       |

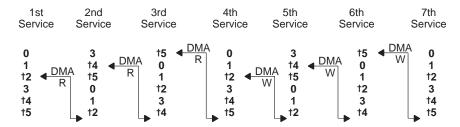

|    |                                                                     |           | Split Mode and DMA Channel Arbitration                     |       |

|    | 11.7                                                                |           | nd DMA Coprocessor Arbitration                             |       |

|    | 11.8                                                                |           | ransfer Modes                                              |       |

|    |                                                                     | 11.8.1    | 3                                                          |       |

|    |                                                                     | 11.8.2    | Running in TRANSFER MODE = 012                             |       |

|    |                                                                     | 11.8.3    | Running in TRANSFER MODE = 102 (Autoinitialization 1)      |       |

|    |                                                                     | 11.8.4    | Running in TRANSFER MODE = 112 (Autoinitialization 2)      | 11-31 |

|    | 11.9  | Autoinitialization                                                |        |

|----|-------|-------------------------------------------------------------------|--------|

|    |       | 11.9.1 Unified Mode                                               |        |

|    |       | 11.9.2 Split Mode                                                 |        |

|    |       | 11.9.3 Incrementing the Link Pointer                              |        |

|    |       | 11.9.4 Synchronization                                            | 11-37  |

|    |       | 11.9.5 Effect on DMA Control Register Bits                        | 11-38  |

|    |       | 11.9.6 Consecutive Autoinitializations                            | 11-40  |

|    | 11.10 | DMA and Interrupts                                                | 11-42  |

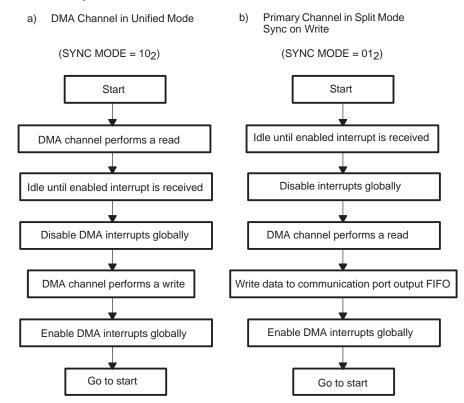

|    |       | 11.10.1 Interrupts and Synchronization of DMA Channels            | 11-43  |

|    |       | 11.10.2 Synchronization Mode Bits                                 | 11-46  |

|    | 11.11 | DMA Memory Transfer Timing                                        | 11-51  |

|    |       | 11.11.1 Single DMA Memory Transfer Timing                         | 11-51  |

|    |       | 11.11.2 DMA Transfer Rate in Synchronization Mode                 | 11-55  |

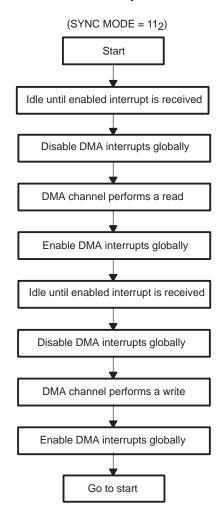

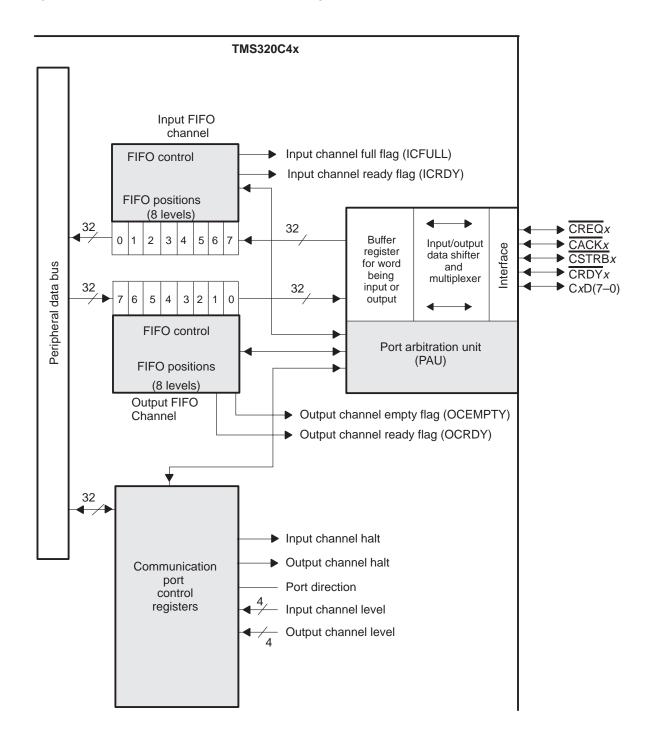

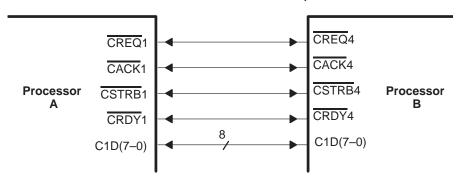

| 12 | Comn  | nunication Ports                                                  | . 12-1 |

|    | Descr | ibes and provides tips for using the communication ports          |        |

|    | 12.1  | Features                                                          |        |

|    | 12.2  | Operational Overview                                              |        |

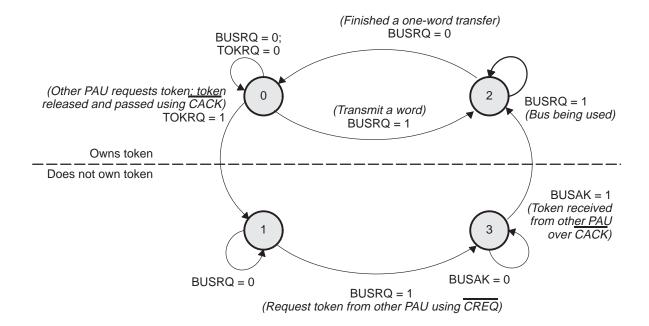

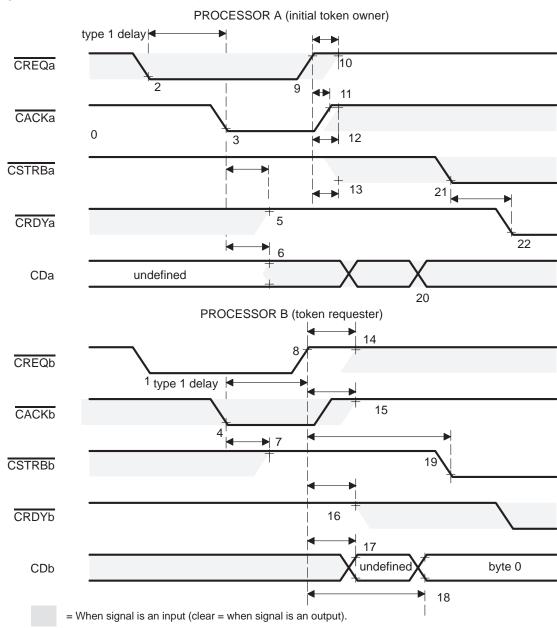

|    |       | 12.2.1 Token Transfer Operation                                   |        |

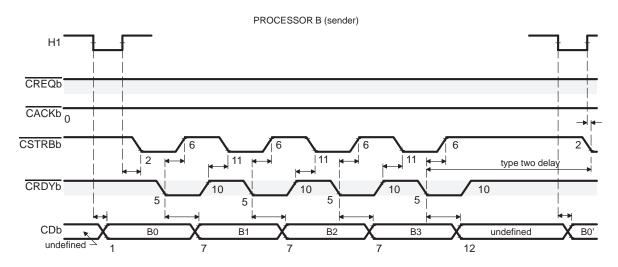

|    |       | 12.2.2 Data Transfer Operation                                    |        |

|    | 12.3  | Memory Map and Registers                                          |        |

|    |       | 12.3.1 Communication-Port Control Register (CPCR)                 |        |

|    |       | 12.3.2 Input-Port Register                                        |        |

|    |       | 12.3.3 Output-Port Register                                       | . 12-9 |